三星电子周四表示,三星电子已成功将3D堆叠技术应用于使用7nm极紫外(EUV)芯片制造工艺制造的测试芯片上。

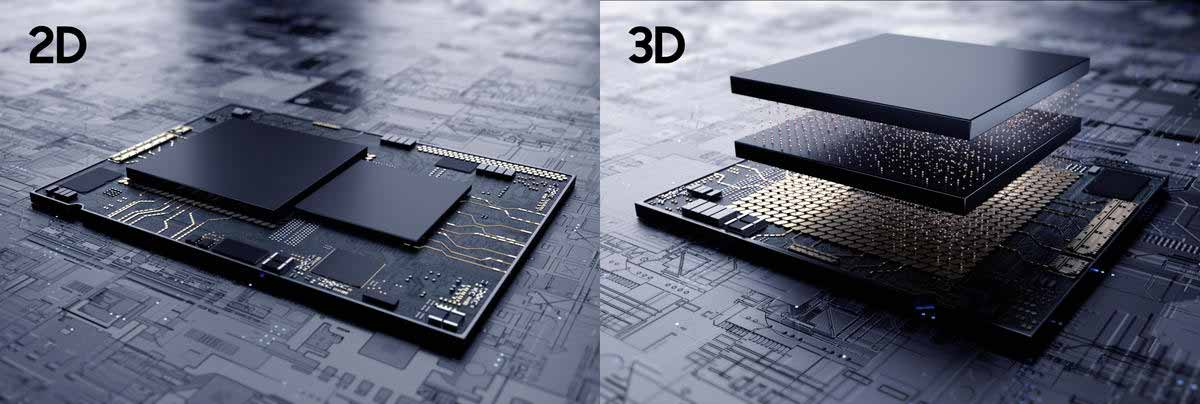

三星被称为扩展立方体(X-Cube),它使用该技术将SRAM堆叠在逻辑芯片的顶部。这与传统方法不同,传统方法是将用于高速缓存的SRAM放置在同一平面上,靠近逻辑芯片(例如CPU和GPU)。

这家韩国科技巨头表示,该技术将允许客户设计占用更少空间的芯片。

三星还将采用其TSV技术,其中存储层和逻辑层的导线通过微小的孔而不是在控制器周围进行连接,从而提高了速度,降低了功耗并允许以更紧凑的方式封装芯片。

三星补充说,这些技术提供的超薄封装设计还使芯片之间的信号路径更短,从而最大程度地提高了数据传输速度和能源效率。

该公司将为客户提供X-Cube的设计方法和流程,以便他们可以开始设计使用EUV工艺制造的7nm和5nm芯片。

客户还将能够使用三星的制造实验室,该公司表示,这将导致更快地发现错误并缩短开发时间。

该公司将在8月16日至18日举行的高性能计算会议Hot Chips上展示该技术。

今年 5月,三星开始为5纳米或更小的芯片建立一条新的EUV代工生产线。它将在明年开始全面运营。

去年,该公司还宣布将 在2030年之前投资133万亿韩元,以加强其逻辑芯片业务。

网友评论文明上网理性发言已有0人参与

发表评论: